# LM3401 **Hysteretic PFET Controller for High Power LED Drive General Description**

The LM3401 is a switching controller designed to provide constant current to high power LEDs. The LM3401 drives an external P-MOSFET switch for step-down (Buck) regulators. The LM3401 delivers constant current within ±6% accuracy to a wide variety and number of series connected LEDs. Output current is adjusted with an external current sensing resistor to drive high power LEDs in excess of 1A.

For improved accuracy and efficiency, the LM3401 features dual-side hysteresis, very low reference voltage, and short propagation delay. A cycle by cycle current limit provides protection against over current and short circuit failures. Additional features include adjustable hysteresis and a CMOS compatible input pin for PWM dimming.

## **Features**

- Hysteretic Control for Speed and Simplicity

- Input Operating Range of 4.5V-35V

- 1.5MHz maximum switching frequency

- Low 200mV reference voltage

- Programmable current limit

- High speed CMOS compatible enable/dimming

- Adjustable hysteresis

- Input UVLO

- No output capacitor required

- MSOP-8 package

## **Applications**

- LED Driver

- **Battery Charger**

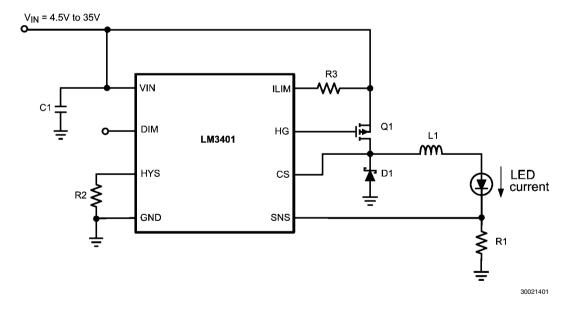

# **Typical Application Circuit**

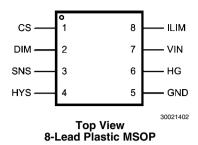

# **Connection Diagram**

# **Ordering Information**

| Part Number | Package Type | NS Package Drawing | Supplied As                 |  |

|-------------|--------------|--------------------|-----------------------------|--|

| LM3401MM    | MSOP-8       | MUA08A             | 1000 Units on Tape and Reel |  |

| LM3401MMX   | IVISOP-0     |                    | 3500 Units on Tape and Reel |  |

# **Pin Descriptions**

| Pin # | Pin Name | Description                                                                                                      |  |

|-------|----------|------------------------------------------------------------------------------------------------------------------|--|

| 1     | CS       | Current sense pin. Connect to the PFET drain                                                                     |  |

| 2     | DIM      | Dimming input pin. When DIM is low, the HG drive is off. Can be connected to a logic level PWM signal            |  |

| 3     | SNS      | Current feedback pin – to LED cathode. Connect a resistor from this pin to ground to set the DC LED              |  |

|       |          | current                                                                                                          |  |

| 4     | HYS      | Hysteresis adjust pin. Connect a resistor from this pin to GND to set the hysteresis window                      |  |

| 5     | GND      | Ground pin                                                                                                       |  |

| 6     | HG       | Gate drive output. Connect to the PFET gate                                                                      |  |

| 7     | VIN      | Power supply input                                                                                               |  |

| 8     | ILIM     | Current limit adjust pin. Connect a resistor from this pin to the PFET source to set the current limit threshold |  |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

VIN -0.3V to 36V CS -2.0V to 36V SNS -0.3V to 8V ILIM -0.3V to 36V DIM -0.3V to 36V HYS -0.3V to 4V Storage Temperature -65°C to +150°C

Lead Temperature

Vapor Phase (60sec) 215°C

Infrared (15sec) 220C

ESD Rating (Note 2)

Human Body Model 2.5kV

## **Operating Ratings** (Note 1)

VIN 4.5V to 35V Junction Temperature Range  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  Thermal Resistance  $\theta_{\text{JA}}$  (Note 3) 151°C/W Power Dissispation (Note 3) 0.66W

**Electrical Characteristics** Specifications in standard type are for  $T_J = 25^{\circ}\text{C}$  only, and limits in boldface type apply over the junction temperature ( $T_J$ ) range of -40°C to +125°C. Unless otherwise stated,  $V_{IN} = 24V$ . Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only (Note 4).

| Symbol                             | Parameter                            | Conditions                              | Min   | Тур   | Max   | Units |

|------------------------------------|--------------------------------------|-----------------------------------------|-------|-------|-------|-------|

| SYSTEM                             | •                                    |                                         |       |       |       |       |

| $V_{REF}$                          | Reference Voltage                    |                                         | 188   | 200   | 212   | mV    |

| $\Delta V_{REF}$ / $\Delta V_{IN}$ | Line regulation                      | 5V < VIN < 35V                          |       | 0.002 |       | mV/V  |

| Ι <sub>Q</sub>                     | Operating VIN Current (Note 5)       |                                         |       | 1.05  |       | mA    |

| I <sub>HYS</sub>                   | Hysteresis Pin Source Current        | HYS pin = 50 mV to 500 mV               | 15    | 20    | 25    | μA    |

| SNS <sub>HYS_MU</sub>              | SNS Comparator Hysteresis Multiplier | HYS pin = 250 mV                        | 0.168 | 0.20  | 0.224 | -     |

| T <sub>DLY</sub>                   | SNS Comparator to HG Delay           | SNS rising                              |       | 46    | 80    | ns    |

| T <sub>DIM</sub>                   | DIM to HG Delay                      | DIM rising                              |       | 69    | 120   | ns    |

| I <sub>ILIM</sub>                  | ILIM Pin Sink Current                |                                         | 4     | 5.5   | 8     | μA    |

| V <sub>CL_OFF</sub>                | Current Limit Comparator Offset      |                                         | -10   | 0     | +10   | mV    |

| V <sub>ZC</sub>                    | Zero Cross Comparator Threshold      | Measured at CS pin                      | -70   | -130  | -200  | mV    |

| $V_{DIM}$                          | DIM Threshold Voltage                |                                         | 1.85  | 2.0   | 2.25  | V     |

|                                    | Hysteresis                           |                                         |       | 286   |       | mV    |

| I <sub>SNS</sub>                   | SNS pin Bias Current                 | V <sub>SNS</sub> = 200 mV               |       | 300   | 780   | nA    |

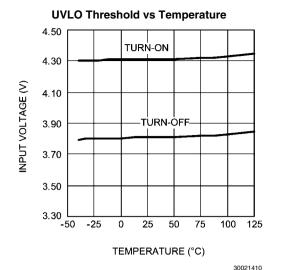

| UVLO                               | UVLO threshold                       | Vin rising                              |       | 4.3   | 4.48  | V     |

|                                    | Hysteresis                           |                                         |       | 0.5   |       | V     |

| DRIVER                             |                                      |                                         |       |       |       |       |

| Ton_min                            | Minimum on-time                      |                                         |       | 150   |       | ns    |

| $R_{HG}$                           | Gate Drive Resistance                | Source Current = 100 mA                 |       | 5.3   |       | Ω     |

|                                    |                                      | Sink Current = 100 mA                   |       | 10.5  |       | Ω     |

| $I_{HG}$                           | Driver Output Current                | Source, HG = VIN -2.5V                  |       | 0.41  |       | Α     |

|                                    |                                      | Sink, HG = VIN -2.5V                    |       | 0.33  |       | Α     |

| $V_{HG}$                           | HG on voltage                        | Referenced to VIN, steady state voltage | -4.2  | -4.7  | -5.5  | V     |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage may occur to the device. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications, see Electrical Characteristics.

Note 3: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J\_MAX}$ , the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{D\_MAX} = (T_{J\_MAX} - T_A)/\theta_{JA}$ . The maximum power dissipation of 0.66W is determined using  $T_A = 25^{\circ}C$ ,  $\theta_{JA} = 151^{\circ}C/W$ , and  $T_{J\_MAX} = 125^{\circ}C$ .  $\theta_{JA}$  will vary with board size and copper area. The  $\theta_{JA}$  spec is based on a JEDEC standard 4-layer board.

Note 4: All room temperature limits are 100% production tested. All limits at temperature extremes are guaranteed through correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 5: IQ specifies the current into the VIN pin and applies to non-switching operation.

Note 2: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin.

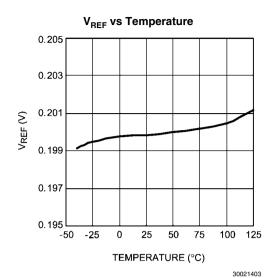

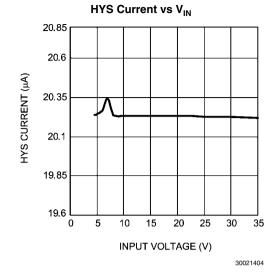

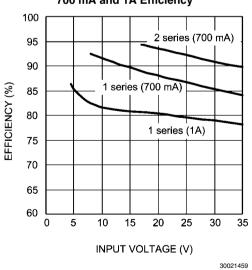

# **Typical Performance Characteristics** Unless otherwise specified, $V_{\text{IN}}$ = 24V, $T_{\text{A}}$ = 25°C.

**HYS Multiplier vs Temperature** 0.23 0.22 HYS MULTIPLIER 0.21 500 mV 0.20 .50 mV-0.19 0.18 125 -50 -25 50 75 100 0 25

TEMPERATURE (°C)

30021406

30021408

1LIM Sink Current vs Temperature

6.0

5.8

5.6

5.4

5.0

5.0

-50

-25

0

25

50

75

100

125

TEMPERATURE (°C)

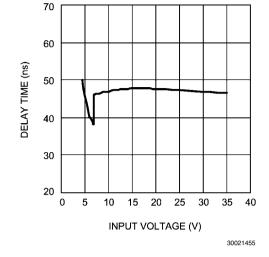

SNS to HG Propagation Delay vs  $V_{\rm IN}$

30021414

300

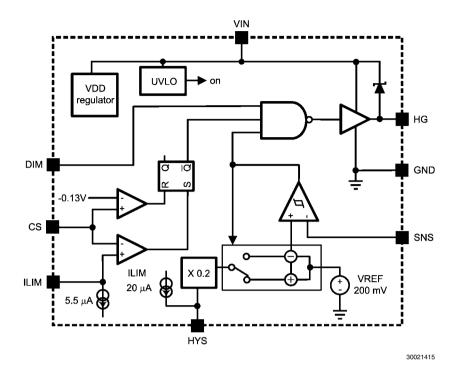

# **Block Diagram**

FIGURE 1. Block Diagram

# **Operational Description**

## **HYSTERETIC CONTROL**

The LM3401 is a step-down DC-DC controller designed to provide a constant current source for driving a high power LED string.

The LM3401 uses comparator-based voltage mode hysteretic control for a simple and stable design. Hysteretic control does not utilize an internal oscillator, but relies on output conditions to directly control switching. The LM3401 controls LED current within the adjustable hysteresis window by monitoring peak and valley voltage at the SNS pin. A dual sided hysteresis window is used to optimize accuracy.

Regulated LED current flows to ground through a sense resistor at the SNS pin. The voltage generated at the SNS pin is compared to the 200 mV internal reference. When the SNS voltage falls below the reference voltage minus hysteresis, the output of the hysteretic comparator goes low. This results in the driver output, HG, pulling the gate of the PFET low and turning on the PFET.

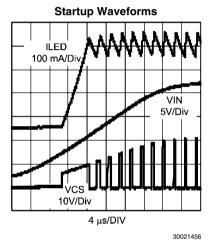

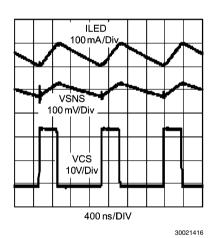

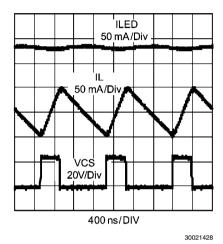

With the PFET on, LED current ramps up through the PFET and the inductor. As the LED current increases, the SNS voltage reaches its upper threshold (reference voltage plus hysteresis). This forces the output of the comparator and HG to go high, which turns the PFET off. When the PFET turns off, current flows through the catch diode, and LED and inductor current ramp down. When the SNS voltage falls to its lower threshold, the cycle repeats. The resulting LED current, SNS, and switch node waveforms are shown in *Figure 2*.

FIGURE 2. Hysteretic Switching Waveforms

#### **OUTPUT CURRENT SETTING**

The LED average current is programmed using a resistor between SNS and GND, shown as R1 in the typical application schematic. The SNS resistor ( $R_{\rm SNS}$ ) can be calculated as follows:

$$R_{SNS} = \frac{V_{SNS}}{I_{LED}}$$

Where  $V_{SNS}$  is 200 mV typically, and  $I_{LED}$  is the DC average LED current

The sense resistor power rating must be higher than its power dissipation. The required power rating can be calculated (in Watts) as follows:

$$W_{RSNS} = V_{SNS} \times I_{LED}$$

When selecting a sense resistor, thermal de-rating must also be taken into consideration.

While  $R_{SNS}$  sets the DC LED current, the AC peak LED current will be higher than the DC setting. This peak current must not be greater than the maximum peak current rating of the LED,  $I_{LED\_max}$ . Peak LED current can be calculated from the equation below:

$$I_{\text{LED\_PK}} = I_{\text{LED}} + \frac{I_{\text{LED\_RIP}}}{2}$$

The LED ripple current,  $I_{\text{LED\_RIP}}$ , is described below in the Hysteresis Adjust section.

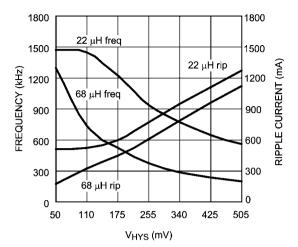

### **HYSTERESIS ADJUST**

Adjustable hysteresis (via the HYS pin) provides direct control over the LED ripple current. The HYS pin also gives some control over the switching frequency. Although the hysteresis value can be set after the inductor is selected, a preliminary value must be set in order to begin the frequency calculation. The hysteresis window must be set small enough to keep the peak LED current below its maximum rating, I<sub>LED max</sub>.

The maximum SNS pin hysteresis can be calculated as shown:

$$SNS_{HYS\ MAX} = (I_{LED\ max} - I_{LED}) \times R_{SNS}$$

Any  ${\rm SNS}_{\rm HYS}$  value between 10mV and this maximum is acceptable.

The  ${\rm SNS_{HYS}}$  value is set with a single resistor from the HYS pin to GND, shown as R2 in the typical application schematic. The HYS pin voltage,  ${\rm V_{HYS}}$ , is internally multiplied by  ${\rm SNS_{HYS}}$  MU (0.2 typical) to generate the hysteresis at the SNS pin,  ${\rm SNS_{HYS}}$ . The hysteresis setting resistor can be determined from the following equation:

$$R2 = \frac{SNS_{HYS} \times 5}{20 \ \mu A}$$

Where 20  $\mu$ A is the typical HYS source current, and SNS<sub>HYS</sub> is the resulting SNS pin hysteresis voltage. The hysteresis voltage can be set within a range of 10 mV to 100 mV (50 mV to 500 mV at the HYS pin). The SNS<sub>HYS</sub> value defines both the upper and lower threshold of the SNS pin. For example, with a V<sub>HYS</sub> setting of 100 mV, SNS<sub>HYS</sub> will be 20 mV. Therefore, the total hysteretic window will be 40 mV, or 20 mV above and 20mV below the 200 mV reference voltage. This directly correlates to peak-to-peak inductor and LED ripple current, approximated by the following equation:

$$I_{LED\_RIP} = \frac{SNS_{HYS} \times 2}{R_{SNS}}$$

If LED ripple current is a design priority, the preliminary R2 value can be determined using a target LED ripple current as shown:

$$R2 = \frac{I_{LED\_RIP} \times R_{SNS} \times 5}{40 \ \mu A}$$

A more precise equation for ripple current is given in the Inductor Selection section. Once an inductor is selected the

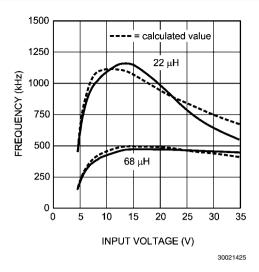

more precise equation should be used to determine the actual ripple current and LED peak current. Larger hysteresis values will result in lower switching frequency and higher ripple current for a given inductor. Typical examples are shown in *Figure 3* below.

30021422

FIGURE 3. Switching Frequency and Ripple Current vs Hysteresis

#### **SWITCHING FREQUENCY**

Although hysteretic control is a simple control method, the switching frequency depends on application conditions and components. If the inductance, input voltage, or LED forward voltage is changed, there will be a change in the switching frequency. Therefore, care must be taken to select components which will provide the desired frequency range. Usually, the best approach is to determine a nominal switching frequency for the application and then select the inductor accordingly. Once the inductor is selected, V<sub>HYS</sub> can be adjusted to set the frequency range more precisely. This design process usually involves a few iterations to select appropriate standard values that will result in the desired frequency and ripple current.

Switching frequency can be approximately calculated using the formula:

$$f_{SW} = \frac{D}{\frac{2 \times SNS_{HYS} \times L}{R_{SNS} \times (V_{IN} - V_{ANODE})} + (2 \times delay)}$$

Where D is the duty cycle, defined as  $(V_{OUT} + V_{DIODE}) / V_{IN}$ ,  $V_{ANODE}$  is 200 mV plus the sum of LED forward voltages, and delay is the sum of the LM3401 propagation delay time and the PFET delay time. The LM3401 propagation delay is 46 ns typically (See the Propagation Delay curve). Alternately, the inductor value can be calculated from a known frequency by re-arranging the same equation:

$$L = \frac{\left[\frac{D}{f_{SW}} - (2 \text{ x delay})\right] \times R_{SNS} \times (V_{IN} - V_{ANODE})}{2 \times SNS_{HVS}}$$

Switching frequency for a typical application is shown in *Figure 4* along with the calculated frequency.

7

FIGURE 4. Frequency vs Input Voltage

Maximum switching frequency will typically occur around the input voltage which corresponds to 25% duty cycle.

If the input voltage falls below the forward voltage of the LED string, the LM3401 will operate at 100% duty cycle. In this state, the anode voltage will be equal to the input voltage and LED current is determined by the v-i curve of the LED. At 100% duty cycle, LED current will be continuous with a maximum value equal to the  $I_{\rm LED\ PK}$  level set at the HYS pin.

In some applications, maximum operating frequency will be limited by the minimum on-time as shown in the following equation:

$$t_{on} = \frac{D}{f_{sw}}$$

When the on-time reaches minimum (150 ns typical) due to increasing input voltage, the frequency will be reduced in order to maintain the proper duty cycle.

### **INDUCTOR SELECTION**

The most important parameters for the inductor are the inductance and the current rating. The LM3401 operates over a wide frequency range and can use a wide range of inductance values.

Once an inductance value is determined from the frequency equation, the maximum operating current must be verified.

Although peak-to-peak ripple current is controlled by the hysteresis value, there is some variation due to propagation delay. This means that the inductance has a direct effect on LED current line regulation.

In general, a larger inductor will result in lower frequency and better line regulation. The actual peak-to-peak inductor current can be calculated as follows:

$$I_{\mathsf{LED\_RIP}} = I_{\mathsf{L\_RIP}} = \frac{2 \times \mathsf{SNS}_{\mathsf{HYS}}}{\mathsf{R_{\mathsf{SNS}}}} + \frac{(\mathsf{V_{\mathsf{IN}}} - \mathsf{V}_{\mathsf{ANODE}}) \times 2 \times \mathsf{delay}}{\mathsf{L}}$$

Use the maximum value of Vin to determine the worst case  $I_{LED\_RIP}$  value. This value should be used to determine the peak current,  $I_{LED\_PK}$ , shown in the Output Current Setting section.

Since the LM3401 can operate at 100% duty cycle, the inductor must be rated to handle  $I_{\text{LED\_PK}}$  continuously.

#### RIPPLE REDUCTION CAPACITOR

The typical application schematic shown on the front page is the simplest application of the LM3401. In this schematic, inductor current is equal to LED current. Therefore, the equations for ripple current apply to both LED ripple and inductor ripple.

However, LED ripple current can be reduced without altering the inductor current by using a bypass capacitor placed in parallel with the LED string (shown as C2 in the *Figure 11* schematic).

This allows larger hysteresis values to be used while significantly reducing ripple current in the LED string. *Figure 5* below shows this effect: inductor ripple current is unaffected while LED ripple current is dramatically reduced.

FIGURE 5. LED Ripple Current Reduction with a 1 μF Ripple Reduction Capacitor

If a ripple reduction capacitor is used, the equation for  ${\rm SNS}_{\rm HYS~MAX}$  only applies for 100% duty operation.

LED average DC current and peak inductor current are not affected by the ripple reduction capacitor. However, LED peak current is reduced and switching frequency may shift slightly.

Any type of capacitor can be used, provided the working voltage rating is sufficient. In general, higher capacitance and lower ESR will provide more ripple reduction; a typical value greater than 100 nF is recommended. Smaller capacitance values will be less effective, and large ESR values may actually increase LED ripple current.

Despite its effectiveness to smooth LED ripple current, there are two notable disadvantages to using a ripple reduction capacitor.

First, when used, care must be taken to avoid shorting the LED anode to ground. If this occurs, the capacitor will force a large negative voltage spike at the SNS pin which could damage the IC.

Second, this capacitor will limit the maximum PWM dimming frequency because it takes some additional time to charge and discharge. Additionally, ceramic capacitors can generate audible noise due to fast voltage changes during dimming. To reduce audible noise, use the smallest possible case size, use dimming frequencies below 500 Hz, or use a non-ceramic ripple reduction capacitor.

A small bypass capacitor, in the range of 100 pF to 200 pF can also be used to reduce high frequency switching noise. This is recommended in higher current applications, where

switching noise can adversely affect the SNS or DIM pins. A small capacitor for noise reduction will have little to no effect on the LED ripple current or dimming but may help solve potential EMI problems.

### **HG AND PFET SELECTION**

When switching, the HG pin swings from  $V_{\rm IN}$  (off state) to 4.7V below  $V_{\rm IN}$  (typical). As long as the DIM pin is high and the SNS pin is below the upper threshold, HG will stay low, driving the PFFT on

The PFET should be selected based on the maximum Drain-Source voltage ( $V_{DS}$ ), Drain current rating (Id), maximum Gate-Source voltage ( $V_{GS}$ ), on-resistance ( $R_{DS(on)}$ ), and Gate capacitance.

The voltage across the PFET in the off state is equal to the sum of the input voltage and the diode forward voltage. The  $V_{\rm DS}$  must therefore be selected to provide some margin beyond this voltage.

Since the peak current through the PFET is equal to the peak current through the inductor, Id must be rated higher than the maximum  $I_{\text{LED\_PK}}$ . The LM3401 is capable of 100% duty cycle, therefore, the PFET drain current should be rated to handle  $I_{\text{LED\_PK}}$  continuously. In this case there is no ripple, so  $I_{\text{DK}} = I_{\text{AVE}}$ .

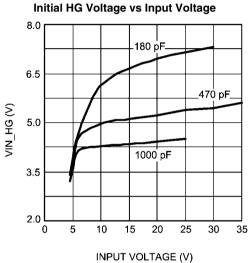

Although the typical HG voltage is  $V_{IN}$  - 4.7V, this voltage can go much lower during the initial PFET turn-on time. How far HG swings at turn-on depends on several factors including the gate capacitance, on-time, and input voltage. As shown in the Typical Performance Characteristics, the initial HG voltage swing increases with decreasing PFET gate capacitance. Therefore, A PFET must be selected with a maximum  $V_{GS}$  rating larger than the initial HG voltage. Conversely, when driving PFETs with larger gate capacitance, the initial HG voltage will be lower. In some cases, a low  $V_{GS}$  threshold PFET may be required to ensure complete turn-on. Use the Typical Performance curve as a guideline to selecting a proper PFET.

Note that HG will eventually settle around the typical voltage of  $\rm V_{IN}$  - 4.7V regardless of the PFET gate capacitance.

HG has an absolute minimum voltage of 1.2V typically. When the input voltage is below approximately 6V, this minimum limit causes a reduction in drive voltage. At 5V input, for example, HG will swing to 1.2V (or a gate drive voltage of -3.8V). This may not be sufficient to drive some PFETs, and at this reduced HG voltage,  $R_{\rm DS(on)}$  is likely to increase and trigger current limit. Therefore, a low  $V_{\rm GS}$  threshold PFET is also recommended for lower input voltage applications.

The power loss in the PFET consists of switching losses and conducting losses. Although switching losses are difficult to precisely calculate, the equations below can be used to estimate total power dissipation, which is the sum of  $\mbox{PD}_{\mbox{COND}}$  and  $\mbox{PD}_{\mbox{SW}}.$

$$PD_{FET\ COND} = R_{DS(on)} \times I_{LED}^2 \times D$$

$$PD_{FET\_SW} = \frac{f_{SW} \times I_{LED} \times V_{IN} \times (P_{on} + P_{off})}{2}$$

Where  $P_{on}$  = PFET turn-on time,  $P_{off}$  = PFET turn-off time, and D is the duty cycle. A value of 10 ns to 50 ns is typical for  $t_{on}$  and  $t_{off}$ . Longer PFET on and off times will degrade both efficiency and accuracy.

Increasing  $R_{DS(on)}$  will increase power losses and degrade efficiency. FET  $_{RDS(on)}$  has a positive temperature coefficient. At 125°C, the  $R_{DS(on)}$  may be as much as 150% higher than the

value at 25°C. The Gate capacitance of the PFET has a direct impact on both PFET transition time and the power dissipation in the LM3401. Most of the power dissipated in the LM3401 is used to drive the PFET switch. This power can be calculated as follows:

The average amount of gate driver current required during switching  $(I_G)$  is:

$$I_G = Q_q \times f_{SW}$$

Where  $Q_q$  is the PFET gate charge.

And the total power dissipated in the IC is:

$$PD = (Iq x V_{IN}) + (I_G x 4.7V)$$

Where Iq is typically 1.05 mA and 4.7V is the typical HG voltage.

Maximum power dissipation within the LM3401 is limited by ambient temperature. Use the following equation to determine maximum allowable power dissipation, or maximum allowable ambient temperature:

$$PD_{max} = \frac{(125^{\circ}C - T_{a_{max}})}{\theta_{1A}}$$

Where  $\theta_{JA}$  is the typical thermal resistance of 151°C/W. In general, keeping the gate capacitance below 2000 pF is recommended to keep propagation delay, switching losses, and power losses low. PFETs with very fast rise times may cause excessive ringing at the HG node when combined with the inductance of a long HG trace. To reduce this ringing, a small resistor can be added between HG and the PFET gate. A typical value of  $10\Omega$  is usually sufficient.

#### **CURRENT LIMIT OPERATION**

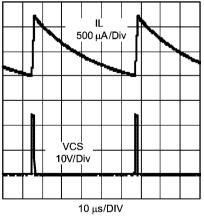

The LM3401 current limit monitors inductor current at each switching cycle. Current is sensed across the  $R_{DS(on)}$  of the PFET at the CS pin. When the PFET current exceeds the current limit threshold, HG is turned off and the current limit latch is set. In current limit mode, the PFET is held off until the inductor current falls to near zero.

30021431

FIGURE 6. Typical Current Limit Operation

The current limit threshold is adjusted with a setting resistor, shown as R3 in the typical application schematic, connected from  $I_{\text{LIM}}$  to the  $V_{\text{IN}}$  node of the PFET.

An internal  $5.5 \,\mu\text{A}$  (typical) current sink at the ILIM pin creates a voltage across the setting resistor. This voltage is compared

9

to the sensed voltage at the CS pin. Current limit is activated and latched when the voltage at the CS pin drops below the voltage at the ILIM pin.

The current limit setting resistor, R3, can be calculated from the equation below. The minimum current limit occurs at maximum  $R_{\rm DS(on)}$  and minimum  $I_{\rm ILIM}$  value.

$$R3 = \frac{I_{LIM\_PK} \times R_{DS(on)}}{4 \mu A}$$

Where 4  $\mu$ A is the minimum I<sub>ILIM</sub> value and I<sub>LIM\_PK</sub> is the peak inductor current limit threshold. I<sub>LIM\_PK</sub> should be set somewhat higher than the maximum LED current, I<sub>LED\_PK</sub>, to avoid false current limit triggering. The temperature variation of the PFET R<sub>DS(on)</sub> will result in an equivalent variation in current limit. To ensure that current limit is not falsely triggered, use the highest R<sub>DS(on)</sub> value over the temperature range to set the R3 value.

When current limit is activated, the HG driver remains off until the CS voltage rises to -130 mV (typical). This ensures that inductor current is close to 0A when the current limit latch is released. The actual minimum inductor current will depend on the catch diode forward voltage characteristic, which determines the CS pin negative voltage.

Although the LM3401 monitors voltage at the CS pin to reset the current limit, there is also a minimum off time of typically 3 µs. When current limit is triggered, HG will be turned off for at least this amount of time, regardless of the inductor current.

The current limit comparator imposes typically 150 ns of blanking time at the beginning of each switching cycle. This ensures that the PFET is fully on and any switch node ringing has dissipated when the current is sensed. However a slower PFET may not fully turn on within the blanking time. In this case, the current limit threshold must be increased or a faster PFET must be used.

Because the current limit comparator has a limited differential voltage capability, a maximum of  $1M\Omega$  is recommended for R3.

## **PWM DIMMING**

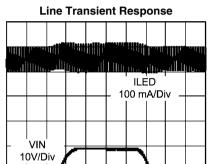

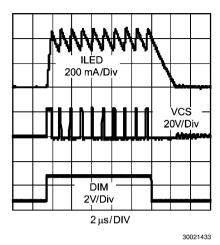

The DIM pin is a CMOS compatible input for a PWM (Pulse Width Modulation) dimming signal. PWM dimming adjusts LED brightness by varying the duty cycle, which varies the average LED current. This type of dimming is recommended, because LED peak current remains constant regardless of brightness, which results in more predictable LED color and performance as compared to analog dimming. *Figure 7* shows a typical PWM dimming waveform.

When DIM is high (above 2V typically) the LM3401 operates normally and the LED string will be driven at the set current. When pulled low, DIM will disable HG and switching will stop. The PFET will remain off as long as DIM is low. When the LM3401 is powered up or enabled with the DIM pin, the LED current will very rapidly increase to its set point.

There is minimal delay time between a DIM logic change and HG switching. Also, because the LM3401 requires no output capacitor, minimal time is required to ramp-up the LED current. This allows for low duty cycle, high frequency PWM dimming signals to be used.

A dimming frequency greater than 100 Hz is recommended to avoid visible flicker. The LM3401 is capable of PWM dimming frequencies up to 10 kHz with a duty cycle between 1 and 100%. Any DIM signal pulse width longer than 100 ns can be used. In most cases, the maximum dimming frequency is

limited by the inductor size and input voltage to anode voltage ratio. Less inductance and higher  $V_{IN}/V_{ANODE}$  ratios will allow the inductor and LED current to increase faster, thus allowing for a faster PWM frequency, or lower dimming duty cycle.

FIGURE 7. Typical PWM DIM Signal and LED Current  $L=22~\mu H$

DIM is a high impedance pin, which is somewhat sensitive to noise. If there is excessive switching noise at the DIM pin, a small bypass filter capacitor can be used. See the Ripple Reduction Capacitor section.  $V_{\rm IN}$  can also be used for PWM dimming when a logic signal is not available. In this mode of operation DIM should be connected to  $V_{\rm IN}$  through a 10  $k\Omega$  resistor. There is typically 10 us of startup delay time when using  $V_{\rm IN}$  for dimming. Depending on the application, this delay limits the maximum dimming frequency to typically several hundred Hz.

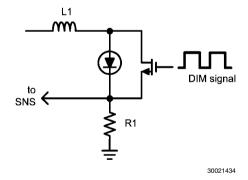

Higher dimming frequency and lower dimming duty cycle can be achieved by using a FET switch in parallel with the LED string. This is shown in *Figure 8* below.

FIGURE 8. Parallel FET Dimming

When the FET switches on, inductor current flows through the FET and the regulated average inductor current is unchanged. Using this method, inductor current rise time does not limit the dimming frequency. A ripple reduction capacitor should not be used with the parallel FET dimming method since it significantly slows the LED current rise time. However, a small noise filter capacitor can be used.

## INPUT CAPACITOR SELECTION

An input bypass capacitor is required between  $V_{\rm IN}$  and ground. The input capacitor prevents large voltage transients

at the input and provides the instantaneous current when the PFET turns on. The important parameters for the input capacitor are the voltage rating and the RMS current rating. Follow the manufacturer's recommended voltage de-rating. RMS current can be calculated with the equation below. The highest RMS current will occur around 50% duty cycle.

$$I_{\text{rms}} = I_{\text{LED}} x \sqrt{\frac{V_{\text{ANODE}}}{V_{\text{IN}}} x \left(1 - \frac{V_{\text{ANODE}}}{V_{\text{IN}}}\right)}$$

A ceramic input capacitor must be placed close to the drain of the PFET. This minimizes the trace inductance between  $V_{\text{IN}}$  and the PFET, which is a source of switching noise. If the input capacitor is not properly located, switching noise can cause current limit and stability problems.

#### **CATCH DIODE SELECTION**

The catch diode provides the current path to the LED string during the PFET off-time and must be rated higher than the average current through the diode, which can be calculated as shown:

$$I_{DIODE} = I_{LED} x (1-D)$$

The peak reverse voltage across the catch diode is approximately equal to the input voltage. Therefore, the diode's peak reverse voltage rating should be larger than the maximum input voltage, plus some safety margin.

A Schottky diode is recommended because its low forward voltage maximizes efficiency. For high temperature applications, diode leakage current may become significant and require a higher reverse voltage rating or a low leakage diode to achieve acceptable performance.

## LED CURRENT ACCURACY

The total accuracy of average LED current is affected by several factors, both internal and external to the LM3401. Total static accuracy is the part-to-part variation and can be calculated from the equation below:

$$I_{LED\_Acc\%} = \sqrt{R_{SNS\%}^2 + V_{SNS\%}^2}$$

Where the worst case  $V_{SNS\%}$  is ±6%, and  $R_{SNS\%}$  is the sense resistor accuracy. Because these factors are not correlated, the RSS (root-sum-square) method of calculation is used.

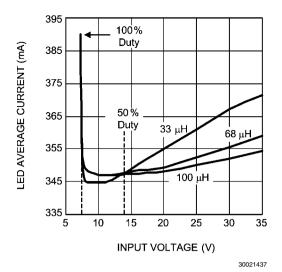

The LED current will also show some variation with input voltage. This is primarily due to propagation delay and the dynamic resistance of the LED. In longer on-time operation, the error due to dynamic resistance tends to dominate, while at shorter on-time, the propagation delay will dominate. These two effects counteract each other, resulting in typical regulation curves similar to those shown in *Figure 9*. A larger inductor will reduce the error due to propagation delay and will result in better overall line regulation.

FIGURE 9. LED DC current line regulation LED Vf = 7.0V

For most applications, the average LED current will be the highest at the maximum input voltage and lowest at a duty cycle somewhat greater than 50%. The maximum LED current variation can be estimated as:

$$I_{LED\_reg} (A) = \frac{(V_{IN\_max} - V_{IN\_60\%}) \times delay}{2 \times L}$$

Where  $V_{\rm IN\_60\%}$  is the input voltage corresponding to a duty cycle of 60%. Since the actual input voltage where minimum LED current occurs varies with the application, this is an approximation. As the duty cycle approaches 100%, the average LED current will approach  $I_{\rm LED\_PK}$ . The average LED current will be the highest at the point that 100% duty cycle is reached. In the case that 100% duty cycle can occur, maximum LED current variation is calculated as:

$$I_{LED\_var\_100\%} (A) = \frac{SNS_{HYS}}{R_{SNS}}$$

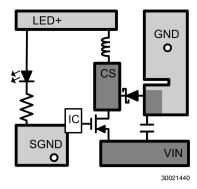

### **PCB LAYOUT**

PCB layout is very important in all switching regulator designs. Poor layout can cause EMI problems, excess switching noise, and improper device operation. The following key points should be followed to ensure a quality layout.

Traces carrying large AC currents should be as wide and short as possible to minimize trace inductance. These areas, shown as darker regions in *Figure 10*, are:

- VIN between the input capacitor and PFET

- GND between the input capacitor and catch diode

- The switch node

As shown in *Figure 10*, place the input capacitor ground as close as possible to the anode of the catch diode. The VIN side of the input capacitor should be placed close to the top of the PFET.

The CS node (the node connecting the catch diode cathode, inductor, and PFET source) should be kept as small as possible. This node is one of the main sources for radiated EMI. The SNS and HYS pins are sensitive to noise. Be sure to route the SNS trace away from the inductor and the switch node, which are sources of noise.

The SNS and HYS resistors should be placed close to their respective pins and grounded close to the GND pin. An isolated ground area shown as SGND in *Figure 10* is recommended for the SNS, HYS, and GND pin connections. The two ground areas, GND and SGND, should be connected on an inner or bottom layer. This connection is shown as two vias in *Figure 10*.

A large, continuous ground plane can also be used, as long as the input capacitor and catch diode ground area is somewhat isolated.

The HG trace should be kept as short as possible to minimize inductance and gate ringing (See HG and PFET selection section).

Finally, for accurate current limit sensing, the CS pin and ILIM resistor connections should be made at the PFET pads, via separate traces.

FIGURE 10. Example PCB Layout

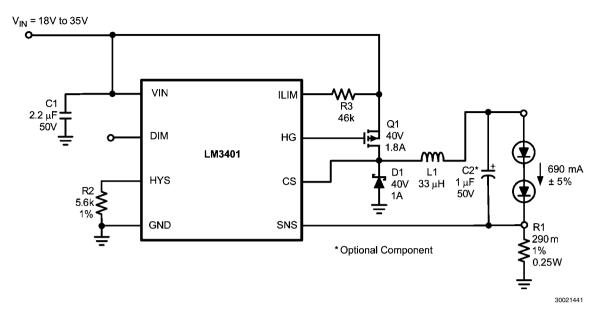

## **Design Example**

FIGURE 11. Example Circuit

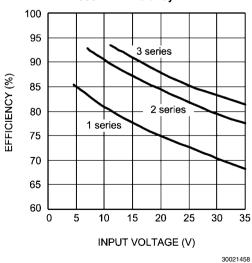

The following design example is intended to illustrate the step-by-step design process described in the previous sections. The example refers to the circuit in *Figure 11*, and the results are summaized in *Table 1*. The resulting circuit will drive a string of 2 Luxeon V Star LEDs at 700 mA from an input voltage between 18V and 35V.

The example LEDs have a maximum DC current rating of 700 mA, a forward voltage of 5.4V to 8.3V, and a maximum peak current rating of 1.0A.

First, set the LED DC current with R1:

$$R1 = \frac{200 \text{ mV}}{700 \text{ mA}} = 286 \text{ m}\Omega$$

And the required wattage is:

$$W_{RSNS} = 700 \text{ mA}^2 \text{ x } 0.286 = 140 \text{ mW}$$

Select a standard value of 290 m $\Omega$ , 1/4W resistor, which will result in a 690 mA LED DC current.

To keep the peak LED current below  $I_{\text{LED\_MAX}}$ , the maximum hysteresis is determined by:

$$SNS_{HYS\ MAX} = (1.0A - .690A) \times 0.29\Omega = 90 \text{ mV}$$

Which gives a maximum R2 value of:

$$R2 = \frac{90 \text{ mV x } 5}{20 \mu A} = 22.48 \text{ k}\Omega$$

Next, a preferred switching frequency of 1 MHz is selected for this example.

Since this is a relatively high switching frequency, a low starting point of 25 mV is selected for the comparator hysteresis to maintain good line regulation. This will allow a larger inductor at the same operating frequency and is well below the calculated maximum. Set a preliminary hysteresis value with R2:

$$R2 = \frac{25 \text{ mV x 5}}{20 \mu A} = 6.25 \text{ k}\Omega$$

For 1 MHz switching frequency and 25 mV hysteresis, inductance can be calculated. Because frequency varies with input voltage and LED forward voltage, for this calculation, assume typical values of 24V and 13.6V respectively, and a PFET delay time of 15 ns.

$$L = \frac{\left[\frac{0.60}{1 \text{ MHz}} - (2 \times 60 \text{ ns})\right] \times [0.29 \times (24 \text{V} - 13.8 \text{V})]}{2 \times 25 \text{ mV}} = 29.6 \text{ } \mu\text{H}$$

Select a value of 33 µH and the hysteresis can be adjusted downward by re-arranging the same frequency equation:

SNS<sub>HYS</sub> =

$$\frac{\left[\frac{0.60}{1 \text{ MHz}} - (2 \times 60 \text{ ns})\right] \times [0.29 \times (24 \text{V} - 13.8 \text{V})]}{2 \times 33 \text{ } \mu\text{H}} = 22.4 \text{ mV}$$

This gives a new R2 value of 5.6k. This will result in a typical operating frequency of 1 MHz at 24V<sub>IN</sub>. Next, it must be verified that the peak LED current is within the maximum allowed. For now, the design is created without using a ripple reduction capacitor. Therefore, LED ripple current is equal to inductor ripple current. Maximum LED ripple current is calculated as:

$$I_{\text{LED\_RIP}} = \frac{2 \text{ x } 22.4 \text{ mV}}{0.29\Omega} + \frac{(35\text{V} - 11\text{V}) \text{ x } 2 \text{ x } 60 \text{ ns}}{33 \text{ } \mu\text{H}} = 227 \text{ mA}$$

Note that the maximum input voltage and minimum anode voltage were used for this worst case calculation.

Now peak LED current can be determined:

$$I_{LED\_PK} = 690 \text{ mA} + \frac{227 \text{ mA}}{2} = 804 \text{ mA}$$

This confirms that the component selections will keep LED peak current below the maximum LED rating. Notice if a ripple reduction capacitor is chosen, the peak inductor current is still 804mA, but the LED peak current is reduced. Therefore, the inductor must be rated for a DC current greater than 804 mA. Now that the inductor value has been selected and verified, the operating frequency range can be determined. Lowest operating frequency occurs at minimum input voltage and maximum anode voltage. For this example the values are 18V minimum input and 16.8V maximum anode voltage (200 mV SNS voltage plus the maximum LED forward voltages) and calculate:

$$f_{SW} = \frac{0.96}{\frac{2 \times 22.4 \text{ mV} \times 33 \mu\text{H}}{0.29\Omega \times (18V - 16.8V)} + (2 \times 60 \text{ ns})} = 219 \text{ kHz}$$

At duty cycles close to 100% (96% in this case) the frequency equation becomes less accurate. Actual switching frequency will typically be lower than the calculated value.

To estimate maximum operating frequency, calculate using a Vin which corresponds to a duty cycle of 25%. In this example, 25% duty cycle would occur above  $35V_{IN}$ , therefore maximum frequency will occur at the maximum input voltage:

$$f_{SW} = \frac{0.41}{\frac{2 \times 22.4 \text{ mV} \times 33 \mu\text{H}}{0.29\Omega \times (35\text{V} - 13.8\text{V})} + (2 \times 60 \text{ ns})} = 1.1 \text{ MHz}$$

Using the equation in the Switching Frequency section, it can be verified that this maximum frequency is within the minimum on-time limited frequency (and below the maximum operating frequency).

The maximum frequency calculation is only an estimate, the actual maximum should be verified on the bench.

The next step is to select a PFET. The critical PFET parameters must meet the minimum circuit requirements of 35V input, 804 mA DC current, and adequate gate drive voltage rating.

Therefore, select a PFET with the following ratings:

40V maximum  $V_{\rm DS}$

-20V maximum V<sub>GS</sub>

1.8A continuous Id

130mohm maximum R<sub>DS(on)</sub>

Typically the PFET may be only sourcing 690 mA for about 50% duty cycle. However, at minimum input voltage the duty cycle will increase close to 100%. Therefore, the PFET Id rating should be based on its continuous, not pulsed, current capability.

Now the power dissipation should be verified. Assume the selected PFET has a gate capacitance of 200 pF, which is within recommendation, and a gate charge of 15 nC. Maximum frequency and input voltage are used for a worst case calculation:

$$I_{G} = 15 \text{ nC x } 1.1 \text{ MHz} = 16.5 \text{ mA}$$

$$PD = (1.05 \text{ mA x } 35\text{V}) + (16.5 \text{ mA x } 4.7\text{V}) = 0.114\text{W}$$

$$T_{a\_\text{max}} = 125^{\circ}\text{C} - (151^{\circ}\text{C/W x } 0.114\text{W}) = 108^{\circ}\text{C}$$

With the selected components, the maximum ambient temperature is above 100°C, sufficient for most applications. Note that this limit applies to the IC only and depends on the pcb type and size. Lower ambient temperature limits may apply to the PFET and other components.

Now the current limit threshold is set with R3 at 0.95A, which is 120% of the maximum peak current. The worst case  $R_{DS}$   $_{(\text{on})}$  value at 125°C is used, which is 150% of nominal, and the worst case ILIM pin sink current.

$$R3 = \frac{0.95A \times 195 \text{ m}\Omega}{4 \text{ }\mu\text{A}} = 46.3 \text{ k}\Omega$$

The typical current limit threshold will be higher than 1A and can be determined by using typical values for  $R_{\rm DS(on)}$  and  $I_{\rm LIM}$  sink current. The PFET, inductor, and catch diode must be able to handle this current for short periods of time.

The next component is the input capacitor, C1. A low ESR ceramic capacitor must be used and properly located on the PCB. For this design, the capacitor working voltage must be rated to at least 40V, and 50V is recommended. A 2.2  $\mu F$  input capacitor should be sufficient, assuming a good PCB layout. The worst case input RMS current is calculated below 50% at duty cycle:

$$I_{\text{rms}} = 690 \text{ mA} \times \sqrt{\frac{13.8 \text{V}}{27.6 \text{V}} \times \left(1 - \frac{13.8 \text{V}}{27.6 \text{V}}\right)} = 345 \text{ mA}$$

It must be verified that the selected input capacitor can tolerate this current. An additional bulk capacitor placed at the input voltage connection is also recommended.

Next, select D1, the catch diode. A Schottky diode should be used. The reverse voltage rating must be greater than 35V and the average forward current rating must be greater than:

$$I_{DIODE} = 690 \text{ mA x } (1 - 0.31) = 480 \text{ mA}$$

This calculation assumes the minimum duty cycle, which is maximum input voltage and minimum anode voltage. The diode must also be able to handle peak currents as high as the current limit threshold for short periods. We select a 1A diode to ensure adequate capability over temperature.

If desired, a ripple reduction capacitor can be added at C2 to reduce the LED ripple current. A minimum starting value of 100 nF is recommended for C2, and a value of 1  $\mu F$  will work well in most applications. In case of an open LED failure, the ripple reduction capacitor must be rated to the maximum input voltage of 35V. If C2 is used, LED ripple current is reduced and the calculated maximum R2 value no longer applies as a limit

Finally, check the accuracy. The static accuracy is calculated below using a 1% sense resistor.

$$I_{LED\_Acc\%} = \sqrt{0.01^2 + 0.06^2} = 6.1\%$$

To estimate line regulation, maximum input voltage and 60% duty cycle input voltage is used. For this example 60% duty cycle occurs at (13.6V + 0.2V)/0.60 or 23V input.

$$I_{LED\_reg} = \frac{(35V - 23V) \times 60 \text{ ns}}{2 \times 33 \text{ } \mu\text{H}} = 11 \text{ mA}$$

This is the estimated amount of LED current variation over the input voltage range. If the minimum input voltage was below

17V, the LED current variation would be calculated using the 100% duty cycle equation.

**TABLE 1. Design Example Summary**

| Parameter           | Value               | Result                           | Comment                               |

|---------------------|---------------------|----------------------------------|---------------------------------------|

| R1                  | 290 mΩ              | 690 mA DC                        | 1%                                    |

| R2                  | 5.6 kΩ              | ±22.4 mV hysteresis              | V <sub>HYS</sub> = 112 mV(adjustable) |

| L1                  | 33 μH, >804 mA      |                                  |                                       |

| $f_sw$              | -                   | 1MHz typical                     | 219 kHz min                           |

| I <sub>ripple</sub> | -                   | 227 mA p-p                       | worst case                            |

| I <sub>LED_PK</sub> | -                   | 804 mA                           | worst case                            |

| PFET                | 40V, 1.8A, 130 mΩ   |                                  |                                       |

| R3                  | 46 kΩ               | 0.95A minimum peak current limit | adjustable                            |

| C1                  | 2.2 μF, 50V ceramic | >345 mA rms                      |                                       |

| D1                  | 40V, 1A             |                                  | Schottky                              |

| Accuracy            | ±6.1%               | ±42 mA max variation             | part-to-part                          |

| Regulation          | 1.6%                | 11 mA variation                  | vs VIN                                |

| Ta_max              | 108°C               |                                  | worst case                            |

| C2                  | 1.0 μF, 50V         | LED ripple reduction             | optional                              |

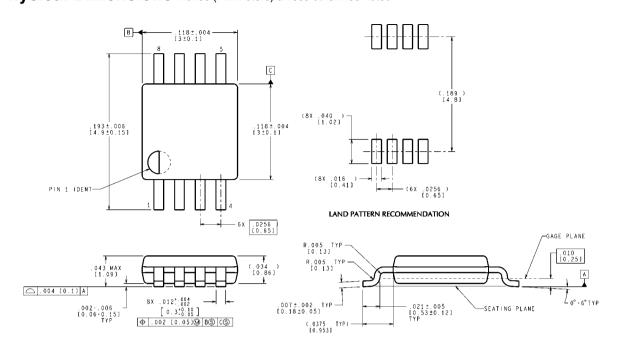

# Physical Dimensions inches (millimeters) unless otherwise noted

CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

MUA08A (Rev E)

8-Lead MSOP Package NS Package Number MUA08A

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Products                       |                              | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: new.feedback@nsc.com

Tel: 1-800-272-9959

Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288

National Semiconductor Europe

National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com